IEEE Reliability Society Newsletter Vol. 61, No. 2, May 2015

Front page:

Society News:

Members & Chapters

Meetings & Conferences

Letters in Reliability

Nihal Sinnudai Shares Lifetime Achievement Award Ideas

Sam Keene's "Lessons Learned in Testing Components"

Links:

Report on 2015 IEEE International Reliability Physics Symposium (IRPS)

Chris Connor , Yuan Chen and Giuseppe LaRosa

2015 IRPS Publicity+Vice Technical Program, Technical Program and General Chairs

IRPS15 held from April 19-23, 2015 at Hyatt Regency Monterey Resort and Spa, Monterey CA, USA serendipitously kicked off exactly on the 50th anniversary of Moore’s Law on April 19th which IEEE had recognized in Spectrum April publication. The key question with respect to reliability – can Moore’s Law continue and not be limited by reliability? IRPS15 technical program kicked off with keynotes by Kaizad Mistry of Intel and Brent Keeth of Micron respectively addressing these topics.

|

|

|

Kaizad Mistry, VP Intel, delivering keynote “Transistors and Reliability in the Innovation Era”. |

||

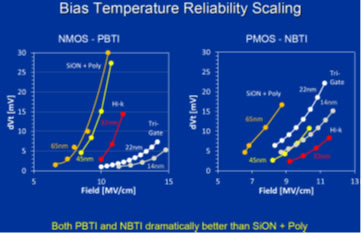

Kaizad Mistry illustrated Dennard’s classical scaling which was applicable through the late 1990’s and how a “golden age of innovation” was occurring with advent of strained silicon, high-K metal gate, and tri-gate (fin-fet) introduction in the 21st century. Improvements in reliability mode data of time dependent dielectric breakdown (TDDB), bias temperature instability (BTI), and soft error were reviewed.

|

BTI reliability scaling by process generation showing effectiveness of innovation in making improvements in reliability with scaling (courtesy Kaizad Mistry, Intel). |

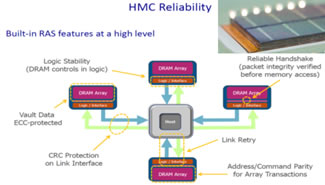

Brent Keeth presented dynamic random access memory (DRAM) performance and scaling, citing the need for a dramatic performance changes to ready 1 TB/s bandwidth, reduced energy consumption of 5mW/GB/s, and x-scale computing of 1018 Flops/s. A radical rethinking of DRAM design to utilize tightly stacked memory in through silicon vias (TSV) coupled with a logic layer to manage the memory and communications with the host which included reliability, availability, and serviceability (RAS) features. These keynotes provided excellent introduction to the technical program and substantial motivation towards continual enabling of reliability aspects of Moore’s Law!

|

|

Brent Keeth, Senior Fellow Micron, delivering keynote “Hybrid Memory Cube (HMC): Achieving High Performance and High Reliability” and Hybrid Memory Cube built in reliability, availability, and serviceability (RAS) features (courtesy Brent Keeth, Micron). |

|

IRPS15 technical program featured reliability topics focusing on the continued advancement of Moore’s Law with several 14nm and many FIN- FET papers from industry leaders. Technical program kicked off with a first-ever combined gate dielectrics and back-end-of-line (BEOL) breakdown session which was highly attended. As dimensions have been scaled continuously, new considerations for interconnect dielectric breakdown must be made in addition to traditional electro-migration reliability. Wednesday evening poster session in the Monterey Grand Ballroom featured over seventy five poster presentations accompanied by delicious dinner selections. Conference proceedings are available in IEEE Explore. The “best of IRPS15” will be announced on Twitter.

IRPS16 will be at Pasadena CA, from April 17-21. Call For Papers has been issued with abstract deadline of October 12, 2015 and late news submissions due January 11, 2016. Please follow on Facebook, Linked-IN, Twitter @IEEEIRPS, and visit http://IRPS.org for latest information. We look forward to seeing you in Pasadena for IRPS16!